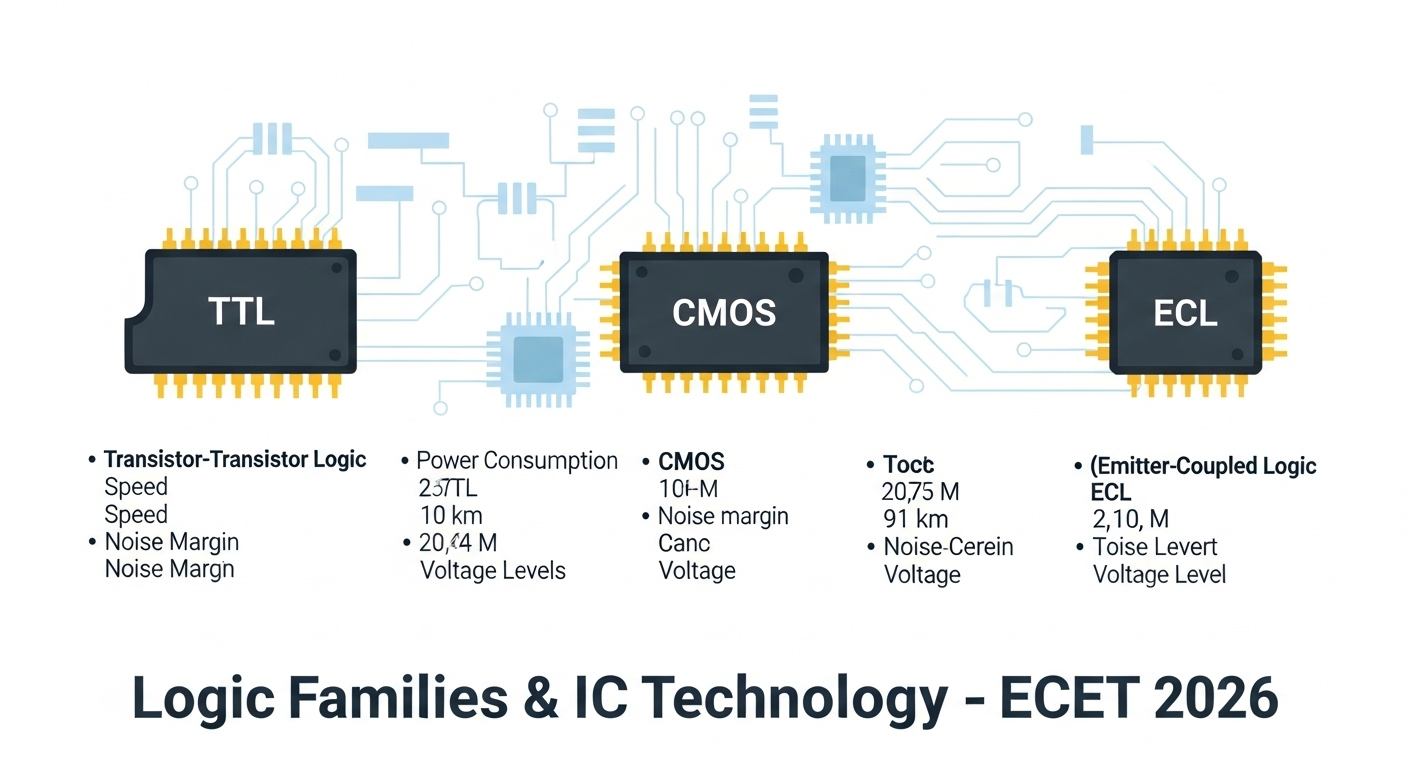

In Digital Electronics (DE), logic families and IC technology are very important topics. ECET exams usually ask direct questions about TTL, CMOS, ECL, fan-out, power dissipation, and IC classifications.

📘 Concept Notes

🌐 Logic Families

A logic family defines the implementation technology used for digital circuits.

Major logic families:

- Diode Logic (DL) – primitive, obsolete.

- RTL (Resistor-Transistor Logic).

- DTL (Diode-Transistor Logic).

- TTL (Transistor-Transistor Logic).

- ECL (Emitter Coupled Logic).

- MOS & CMOS (Complementary MOS).

⚙️ Parameters of Logic Families

- Fan-in: Number of inputs a gate can handle.

- Fan-out: Maximum number of gates a gate output can drive.

- Noise Margin (NM): Ability to tolerate noise.

![]()

![]()

- Propagation Delay (

): Time taken for input change → output change.

): Time taken for input change → output change. - Power Dissipation (P):

![]()

- Speed-Power Product (SPP):

![]()

- Fan-out Calculation:

![]()

🔋 Comparison of Families

| Parameter | TTL | CMOS | ECL |

|---|---|---|---|

| Power Dissipation | High | Very Low | Very High |

| Speed | Medium | Medium–High | Highest |

| Fan-out | 10–20 | >50 | 20–30 |

| Noise Margin | Moderate | High | Low |

🏭 IC Technology

IC Classification by Scale of Integration:

- SSI: Small Scale Integration (<100 gates/chip).

- MSI: Medium Scale Integration (100–1000 gates/chip).

- LSI: Large Scale Integration (1k–10k gates/chip).

- VLSI: Very Large Scale Integration (10k–1M gates/chip).

- ULSI: Ultra Large Scale Integration (>1M gates/chip).

📐 Example

If:

Then Power Dissipation =

![]()

🔟 10 Expected MCQs – ECET 2026

Q1. Which is the fastest logic family?

A) TTL

B) CMOS

C) ECL

D) RTL

Q2. In CMOS, power dissipation is:

A) Very high

B) Very low

C) Same as TTL

D) Same as ECL

Q3. Fan-out is defined as:

A) No. of inputs a gate can accept

B) No. of gates an output can drive

C) No. of logic levels in a system

D) None

Q4. Formula for power dissipation is:

A) ![]()

B) ![]()

C) ![]()

D) ![]()

Q5. Which family has the best noise margin?

A) TTL

B) CMOS

C) ECL

D) RTL

Q6. The speed-power product (SPP) is given by:

A) ![]()

B) ![]()

C) ![]()

D) ![]()

Q7. Which IC technology refers to >1M gates/chip?

A) MSI

B) VLSI

C) LSI

D) ULSI

Q8. Typical TTL fan-out is:

A) 1–2

B) 5

C) 10–20

D) >50

Q9. In IC technology, SSI means:

A) <100 gates

B) 100–1000 gates

C) 1k–10k gates

D) >10k gates

Q10. Which logic family is least affected by noise?

A) TTL

B) CMOS

C) ECL

D) RTL

✅ Answer Key

| Q.No | Answer |

|---|---|

| Q1 | C |

| Q2 | B |

| Q3 | B |

| Q4 | B |

| Q5 | B |

| Q6 | B |

| Q7 | D |

| Q8 | C |

| Q9 | A |

| Q10 | B |

🧠 Explanations

- Q1 → C: ECL is fastest.

- Q2 → B: CMOS has very low static power dissipation.

- Q3 → B: Fan-out is no. of gates driven by one output.

- Q4 → B: Power = Voltage × Current.

- Q5 → B: CMOS has highest noise margin.

- Q6 → B: SPP = Delay × Power.

- Q7 → D: Ultra Large Scale Integration = >1M gates.

- Q8 → C: TTL fan-out = 10–20.

- Q9 → A: SSI = <100 gates/chip.

- Q10 → B: CMOS least affected by noise.

🎯 Why Practice Matters

- Logic Families questions are straightforward and formula-based.

- With a few formulas and comparisons, students can score quick marks.

- IC classification is a repeated concept in ECET exams.